-

Verilog is a Hardware Description Language (HDL) used to design and model digital systems at various levels of abstraction.

-

It supports multiple design styles, including bottom-up and top-down methodologies, making it flexible for simple to complex designs.

-

Understanding behavioral, register-transfer (RTL), and gate-level abstraction is key to mastering Verilog and digital hardware design.

If you want a clear, step-by-step introduction, here’s a helpful video to get started:

What Is Verilog HDL?

When I first started learning about digital design, Verilog was the language that opened the door for me. Simply put, Verilog is a hardware description language-or HDL-that lets you describe digital circuits in code. Think of it like writing software, but instead of telling a computer what to do, you’re telling hardware how to behave.

You can describe anything from a simple flip-flop to a complex microprocessor with millions of gates. That’s the power of Verilog. It’s widely used in industry for designing ASICs (Application-Specific Integrated Circuits) and FPGAs (Field-Programmable Gate Arrays).

One of the biggest advantages is that Verilog lets you describe your design at different levels of abstraction. You don’t have to start at the gate level and get lost in details right away. Instead, you can begin at a higher level, focusing on behavior or data flow, and refine your design as you go.

Design Styles: Bottom-Up vs. Top-Down

When it comes to designing digital systems, there are two common approaches:

-

Bottom-Up Design: This is the traditional method. You start by designing small building blocks, like gates and flip-flops, then combine them to create bigger components. It’s straightforward but quickly becomes unmanageable for large, complex designs.

-

Top-Down Design: Here, you start with the big picture – the overall system – and break it down into smaller modules. This approach allows early testing and easier modifications but can be challenging to implement purely.

In practice, most designs use a mix of both. You might define some modules bottom-up and others top-down, depending on the complexity and project needs.

Levels of Abstraction in Verilog

Verilog supports multiple abstraction levels, and understanding these is crucial for writing effective HDL code.

1. Behavioral Level

At this level, you describe what the system does without worrying about how it’s implemented. You write algorithms that run concurrently, but each algorithm executes sequentially. Behavioral modeling uses constructs like always blocks, functions, and tasks.

For example, you might describe a counter by specifying how it increments on each clock cycle, without detailing the underlying flip-flops.

2. Register Transfer Level (RTL)

This is the sweet spot for most digital designers. RTL focuses on the flow of data between registers and the logical operations performed on that data. It’s more detailed than behavioral but still abstract enough to be manageable.

In RTL, you explicitly define clocked processes and data transfers. This level is synthesizable, meaning synthesis tools can convert your Verilog code into actual hardware gates.

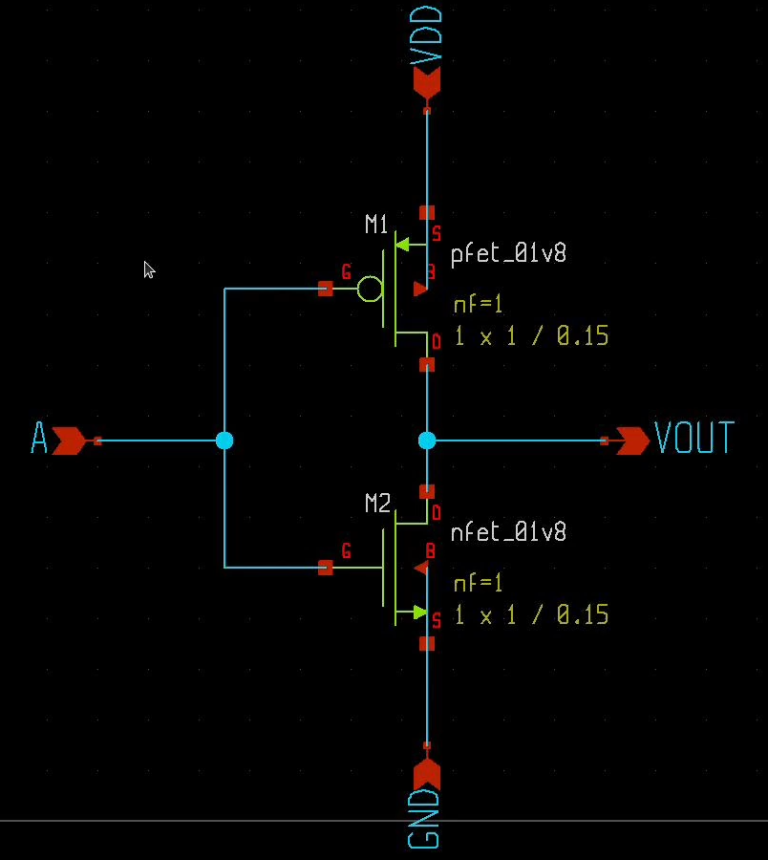

3. Gate Level

At the gate level, you describe the circuit in terms of logic gates and their connections. This is the lowest level of abstraction in Verilog and is usually generated automatically by synthesis tools from RTL code.

Gate-level descriptions are used mainly for simulation and verification after synthesis, not for initial design.

Basic Structure of a Verilog Module

A Verilog design is organized into modules, which are like building blocks. Each module has:

-

Port List: Defines inputs, outputs, and bidirectional ports.

-

Port Declarations: Specifies the direction (

input,output,inout) and size (bit-width) of each port. -

Internal Signals: Variables and nets used inside the module.

-

Behavioral Code: Defines how the module behaves or how signals are processed.

Here’s a simple example of a module declaration:

module simple_and_gate (

input wire a,

input wire b,

output wire y

);

assign y = a & b;

endmodule

This module describes a simple AND gate. The assign statement continuously drives the output y with the logical AND of inputs a and b.

Data Types in Verilog

Verilog has two main data types:

-

Nets: Represent physical connections between hardware elements. They reflect continuous assignments and connections.

-

Variables: Used inside procedural blocks (

always,initial) to store values temporarily.

Common types include:

| Data Type | Description | Usage Example |

|---|---|---|

wire |

Represents a physical wire (net) | Connecting outputs to inputs |

reg |

Holds values in procedural blocks | Storing state in flip-flops |

integer |

For simulation and calculations | Loop counters, temporary variables |

Continuous Assignments vs. Procedural Blocks

Verilog distinguishes between two ways to describe logic:

-

Continuous Assignment: Used for combinational logic. The

assignkeyword drives a net continuously. -

Procedural Blocks: Used for sequential logic and complex behavior. The

alwaysblock is the most common procedural block, triggered by events like clock edges.

Example of an always block for a flip-flop:

always @(posedge clk or negedge reset_n) begin

if (!reset_n)

q <= 0;

else

q <= d;

end

This block describes a positive-edge-triggered flip-flop with asynchronous active-low reset.

Why Learn Verilog?

If you’re interested in digital design, VLSI, or FPGA development, Verilog is essential. It’s the industry standard for describing hardware in a way that’s both human-readable and machine-synthesizable.

Learning Verilog helps you:

-

Design complex digital systems efficiently.

-

Simulate and verify your designs before hardware fabrication.

-

Interface with synthesis tools to generate hardware layouts.

-

Understand the underlying hardware behavior through code.

Tips for Beginners

-

Start simple: Begin with basic combinational circuits like gates and multiplexers.

-

Practice writing modules: Modular design is key to managing complexity.

-

Simulate often: Use simulators to test your code and understand behavior.

-

Understand timing: Learn about clocks, resets, and timing constraints early.

-

Explore design examples: Study open-source Verilog projects to see real-world usage.

Summary Table: Verilog HDL Essentials

| Concept | Description | Example/Notes |

|---|---|---|

| Module | Basic building block of Verilog design | module, ports, internal signals |

| Data Types | Nets (wire), variables (reg) |

Continuous vs. procedural logic |

| Design Styles | Bottom-up, top-down, mixed | Choose based on project complexity |

| Abstraction Levels | Behavioral, RTL, Gate | Behavioral for algorithmic, RTL for synthesis |

| Procedural Blocks | always, initial |

Sequential logic, simulation setup |

| Continuous Assignments | assign statements for combinational logic |

Drives nets continuously |

Key Takeaways

-

Verilog HDL allows you to describe digital hardware at multiple abstraction levels, making it versatile for simple and complex designs.

-

Understanding the difference between behavioral, RTL, and gate-level modeling is essential for effective hardware design and synthesis.

-

Starting with modular, well-structured code and practicing simulation will build a strong foundation in Verilog and digital design.

Verilog is a powerful tool that bridges the gap between hardware concepts and real-world implementations. Once you get comfortable with its syntax and design philosophy, you’ll find it opens up a lot of possibilities in digital system design.